Automaattinen optinen BGA-rework Station

Käytetään laajasti matkapuhelimen, kannettavan tietokoneen, tietokoneen, television, ilmastointilaitteen jne. emolevyn sirutason korjauksessa. Sillä on korkea onnistunut korjausaste ja korkea automaatioaste, mikä säästää paljon ihmisen työtä. Olemme tämän koneen ammattimainen valmistaja ja meillä on näitä koneita varastossa.

Kuvaus

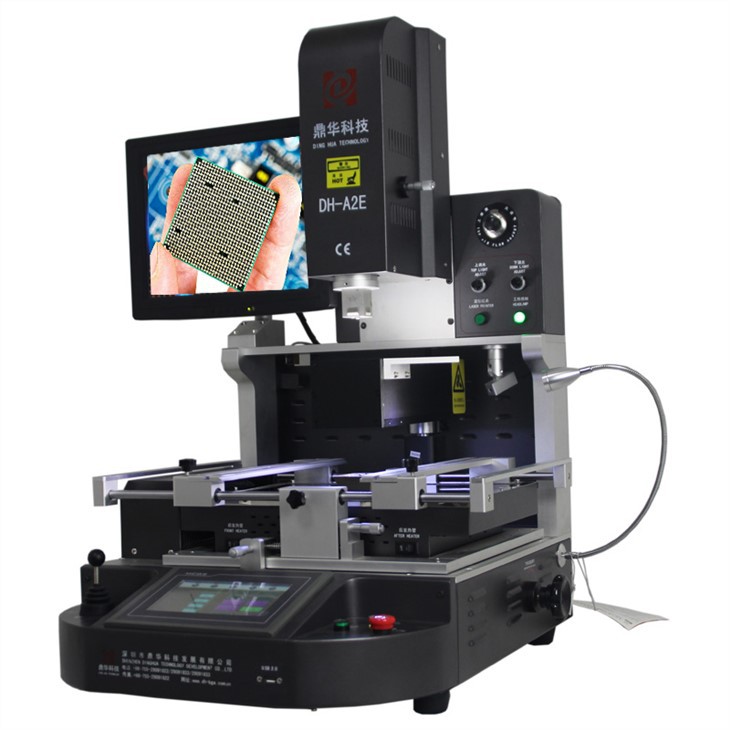

Automaattinen optinen BGA-rework Station

1. Auto Optical BGA Rework Stationin käyttö

Tietokoneen emolevy, älypuhelin, kannettava tietokone, MacBookin logiikkakortti, digitaalikamera, ilmastointilaite, televisio ja muu elektroninen

laitteet lääketeollisuudesta, viestintäteollisuudesta, autoteollisuudesta jne.

Sopii erilaisille siruille: BGA,PGA,POP,BQFP,QFN,SOT223,PLCC,TQFP,TDFN,TSOP,PBGA,CPGA,LED-siru.

2. Auto Optical BGA Rework Stationin tuoteominaisuudet

•Suuri onnistunut sirutason korjausaste. Juotoksen purku, asennus ja juottaminen ovat automaattisia.

• Jokaisen juotosliitoksen tarkka kohdistus voidaan taata optisen kohdistuksen CCD-kameralla.

•Tarkka lämpötilan säätö voidaan varmistaa 3 erillisellä lämmitysalueella. Kone voi asettaa ja tallentaa

1 miljoona lämpötilaprofiilia.

• Kiinnityspäässä oleva sisäänrakennettu tyhjiö poimii BGA-sirun automaattisesti juottamisen jälkeen.

3. Auto Optical BGA Rework Stationin määrittely

4. Auto Optical BGA Rework Stationin tiedot

CCD-kamera (tarkka optinen kohdistusjärjestelmä); 2.HD-digitaalinen näyttö; 3. Mikrometri (säädä sirun kulmaa);

4.3 itsenäistä lämmitintä ( kuumailma ja infrapuna ) ; 5. Laserpaikannus ; 6. HD-kosketusnäytön käyttöliittymä, PLC-ohjaus;

7. Led ajovalaisin ; 8. Joystick-ohjaus.

5.Miksi valita meidän Auto Optical BGA Rework Station?

6. Auto Optical BGA Rework Station -sertifikaatti

7. Auto Optical BGA Rework Stationin pakkaus ja lähetys

8.FAQ

Kuinka testata sirua?

Ensimmäinen järjestelmätason sirutesti

SoC perustuu syviin submikronisiin prosesseihin, joten uusien Soc-laitteiden testaus vaatii täysin uudenlaista lähestymistapaa. Koska jokainen toiminnallinen komponentti

on omat testausvaatimukset, suunnitteluinsinöörin on tehtävä testisuunnitelma suunnitteluprosessin varhaisessa vaiheessa.

SoC-laitteiden lohkokohtainen testisuunnitelma tulee toteuttaa: oikein konfiguroidut ATPG-työkalut logiikkatestausta varten; lyhyet testiajat; uusi nopea

vikamallit ja useat muisti- tai pienryhmätestit. Tuotantolinjalla diagnostiikkamenetelmä ei vain löydä vikaa, vaan myös erottaa sen

viallinen solmu toimivasta solmusta. Lisäksi testimultipleksointitekniikoita tulisi käyttää aina kun mahdollista testiajan säästämiseksi. Alalla erittäin

integroidulla IC-testauksella, ATPG:llä ja IDDQ:n testattavilla suunnittelutekniikoilla on tehokas vikojen erotusmekanismi.

Muita todellisia parametreja, jotka on suunniteltava etukäteen, ovat skannattavien nastojen määrä ja muistin määrä kussakin nastan päässä.

Rajaskannaukset voidaan upottaa SoC:hen, mutta ne eivät rajoitu korttien tai monisiruisten moduulien yhteenliittämistesteihin.

Vaikka sirun koko pienenee, siru voi silti pakata miljoonista 100 miljoonaan transistoria, ja testimoodien määrä on kasvanut ennennäkemättömäksi

tasoilla, mikä johtaa pidempiin testisykleihin. Tämä ongelma voidaan testata. Mode pakkaus ratkaista ,pakkaussuhde voi nousta 20 prosentista 60 prosenttiin . Tämän päivän laajamittaiseen

sirun suunnittelussa kapasiteettiongelmien välttämiseksi on löydettävä testiohjelmisto, joka voi toimia 64-bittisissä käyttöjärjestelmissä.

Lisäksi testiohjelmistot kohtaavat uusia testausongelmia, jotka johtuvat syvien alle mikronin prosesseista ja lisääntyvästä taajuudesta. Aiemmin ATPG-testitila varten

staattisten lukitusvikojen testausta ei enää voitu soveltaa. Toiminnallisten kuvioiden lisääminen perinteisiin työkaluihin vaikeutti uusien vikojen löytämistä. Parempi lähestymistapa on

luokittele aiemmat toimintatilaryhmät määrittääksesi, mitä vikoja ei voida havaita, ja luo sitten ATPG-tila näiden puuttuvien vikatyyppien tallentamiseksi.

Suunnittelukapasiteetin kasvaessa ja transistorin testausajan pienentyessä nopeuteen liittyvien ongelmien löytämiseksi ja piirin ajoituksen tarkistamiseksi synkroninen testausmenetelmä

on palkattava. Synkronisen testauksen on sisällettävä useita vikamalleja, mukaan lukien transienttimallit, polkuviiveet ja IDDQ.

Jotkut alan yritykset uskovat, että esto-, toiminta- ja ohimenevien/polkuviiveiden yhdistäminen voi olla tehokkain testistrategia. Syvälle

submikronin sirut ja suurtaajuustoiminta, transientti- ja polkuviiveen testaus on vielä tärkeämpää.

Testiytimen synkronoinnin ATE-tarkkuuden ongelman ratkaisemiseksi ja kustannusten pienentämiseksi on löydettävä uusi menetelmä, joka yksinkertaistaa

testilaite (transientti- ja polkuviivetesti vaatii tarkan kellon testilaitteen rajapinnassa), Se varmistaa, että signaali on riittävän tarkka testin aikana.

Koska SoC-muistilohkossa on suuri valmistusvirheiden mahdollisuus, muisti BIST:ssä on oltava diagnostiikkatoiminto. Kun ongelma löytyy,

viallinen osoiteyksikkö voidaan kartoittaa varaosoiteyksikön redundanttimuistiin ja havaittu vikaosoite hylätään. Vältä hävittämistä

koko kallis siru.

Pienten sulautettujen muistilohkojen testaus eliminoi lisäporttien tai ohjauslogiikan tarpeen. Esimerkiksi vektorimuunnostestaustekniikat voivat muuntaa

toiminnalliset tilat sarjaksi skannaustiloja.

Toisin kuin BIST-menetelmässä, ohitusmuistilohkon toiminnallinen tulo ei vaadi ylimääräistä logiikkaa. Koska ylimääräistä testilogiikkaa ei tarvita, SoC

kehitysinsinöörit voivat käyttää uudelleen aiemmin luotuja testimalleja.

Kehittyneet ATPG-työkalut eivät vain testaa makroja rinnakkain, vaan myös määrittävät, onko niissä ristiriitoja, sekä yksityiskohtaisesti, mitä makroja voidaan testata rinnakkain ja mitkä

makroja ei voi testata rinnakkain. Lisäksi näitä makroja voidaan testata tehokkaasti, vaikka makrokello olisi sama kuin skannauskello (kuten synkroninen muisti).

Tällä hetkellä tiheällä kaksipuolisella levyllä ei ole tarpeeksi testipisteitä, ja jokainen monimutkainen siru on varustettava rajapyyhkäisypiirillä. Ilman

rajaskannaukset, korttitason valmistusvirheiden haut ovat melko vaikeita, eikä niitä edes löydy. Rajaskannauksella korttitason testaus on erittäin helppoa

ja riippumaton sirun sisällä olevasta logiikkapiiristä. Rajaskannaus voi myös määrittää ATPG-tilan sirun skannausketjuun missä tahansa tuotantovaiheessa.